28+ dual slope adc block diagram

The analog signal is first applied to the sample block where it is sampled at a specific sampling frequencyThe sample amplitude value is maintained and held in the hold block. For a 36V Li cell therefore the output is 20mVV 36V 72mV.

2

The integrator uses a resistor at the input which along with.

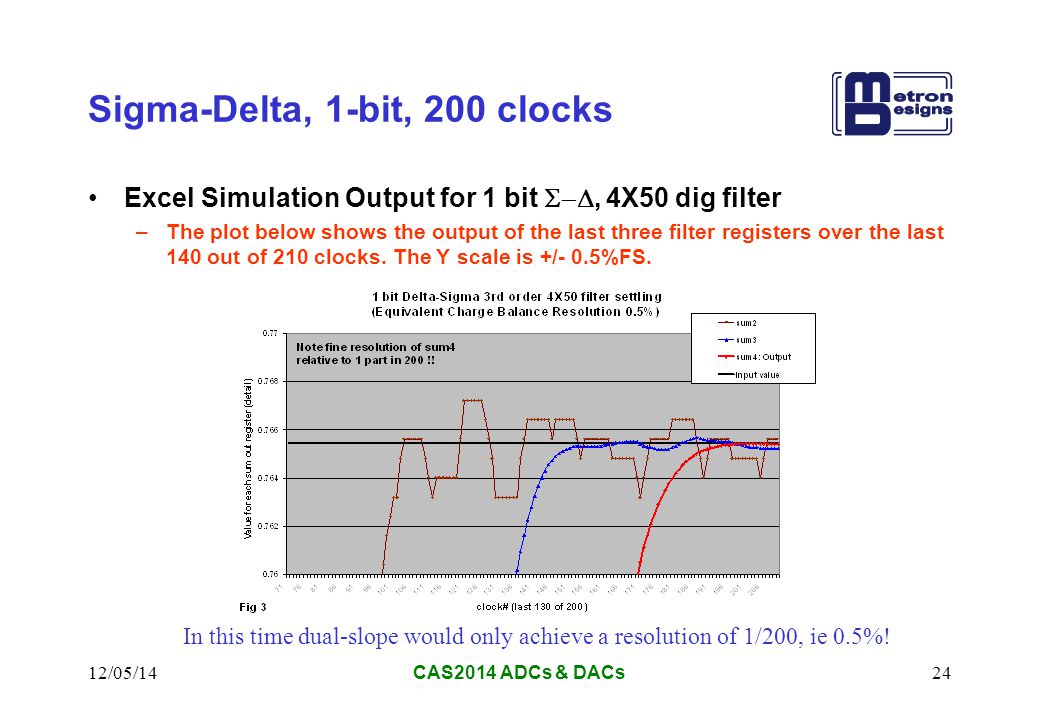

. Dual-slope integration has many. The sensor S1 produces 20mVV at full scale Figure 2. Merit FoMs are 26 fJconversion-step and 1760 dB respec-tively.

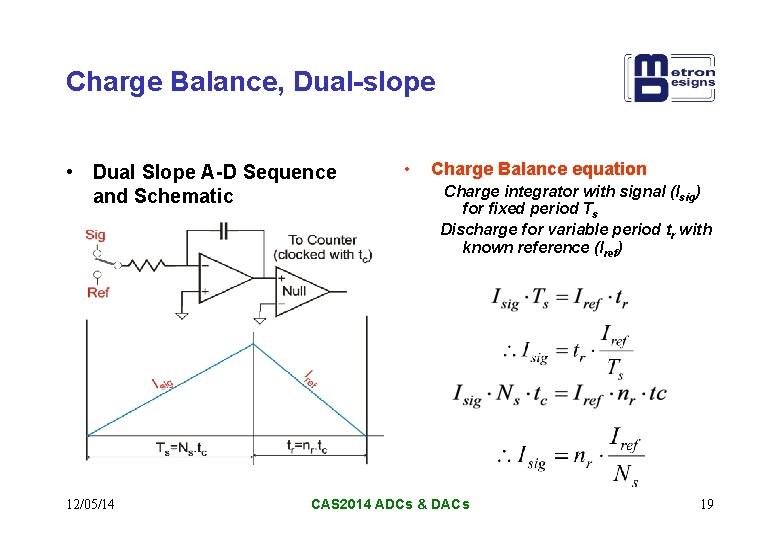

For n bit dual slop type of ADC Vr 2 n N. As the name suggests a dual slope ADC produces an equivalent. Figure-5 depicts block diagram of Dual Slope Integrating type ADC.

Dual Slope ADC Integrator Output Waveforms. Block diagram adclloo 48 47 n1. It is used in the design of digital voltmeter.

The first integration slope differs depending on the value of the input voltage while the second slope is constant and depends on VREF which is itself constant. Diagram is shown in Figure 1 and the integrator output waveforms are shown in Figure 2. Figure 2 Dual-slope ADC block diagram A two-stage op-amp is used in the analog sub-unit as an Integrator and a Comparator.

Timing diagram of a digital-slope ADC. 72 input hold b polarity 9 ready 10 trigger 11 67 analog grd 66 offset 65 overload 64 ref in 1 14 215. This chapter discusses about it in detail.

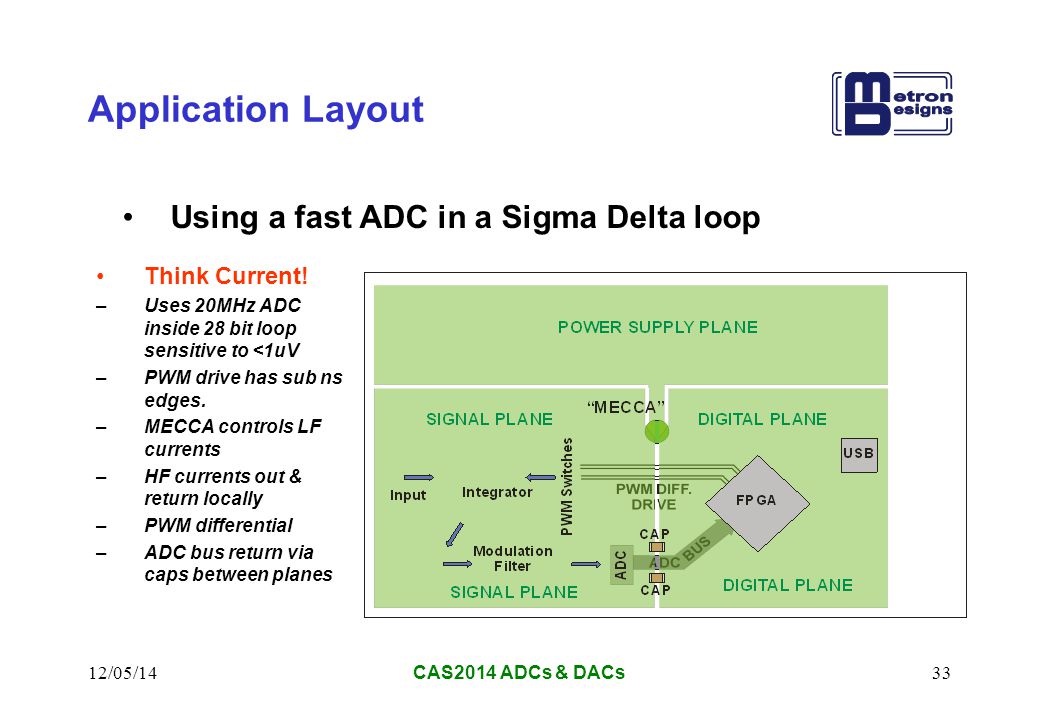

The detailed schematic diagram of the prototype 20-bitlinear AD converter is shown in Figure 2. An Analog to Digital Converter ADC converts an analog signal into a digital signal. Block diagram of an ansychronous digital-slope ADC.

Dual slope integrating type ADC. The digital signal is represented with a binary code which is a combination of bits 0 and 1. Dual slope ADC is the best example of an Indirect type ADC.

For clarity the details of the INS8070 microprocessor and its associated logic are shown in. Block diagram of the slope-ADC calibration circuit. Dual slope aid converters adc-14 i adc-17 i adciioo.

Equal to t 1 the input voltage is disconnected and the integrator input is connected to a negative voltage e r The integrator output will have a negative slope which is constant and.

2

2

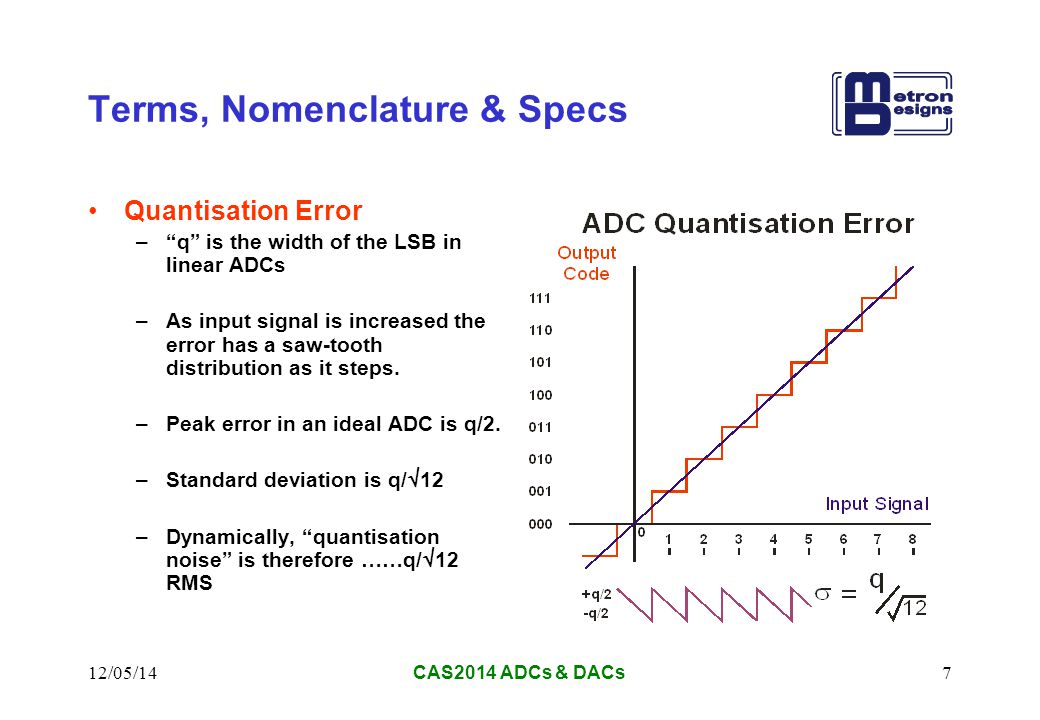

Cern Accelerator School Adcs And Dacs Analogue To

12 05 14cas2014 Adcs Dacs1 Cern Accelerator School Adcs And Dacs Analogue To Digital And Digital To Analogue Converters John Pickering Metron Designs Ppt Download

2

2

2

12 05 14cas2014 Adcs Dacs1 Cern Accelerator School Adcs And Dacs Analogue To Digital And Digital To Analogue Converters John Pickering Metron Designs Ppt Download

12 05 14cas2014 Adcs Dacs1 Cern Accelerator School Adcs And Dacs Analogue To Digital And Digital To Analogue Converters John Pickering Metron Designs Ppt Download

2

12 05 14cas2014 Adcs Dacs1 Cern Accelerator School Adcs And Dacs Analogue To Digital And Digital To Analogue Converters John Pickering Metron Designs Ppt Download

12 05 14cas2014 Adcs Dacs1 Cern Accelerator School Adcs And Dacs Analogue To Digital And Digital To Analogue Converters John Pickering Metron Designs Ppt Download

2

12 05 14cas2014 Adcs Dacs1 Cern Accelerator School Adcs And Dacs Analogue To Digital And Digital To Analogue Converters John Pickering Metron Designs Ppt Download

2

2

12 05 14cas2014 Adcs Dacs1 Cern Accelerator School Adcs And Dacs Analogue To Digital And Digital To Analogue Converters John Pickering Metron Designs Ppt Download